## Vrije Universiteit Brussel Programming Technology Lab Faculty of Sciences Department of Computer Science Academic Year 2000 - 2001

## A Finite State Machine Approach to Real-Time Scheduler Generation for Embedded Systems

Jessie Dedecker jessie.dedecker@vub.ac.be

Promotor: Prof. Dr. Theo D'Hondt

Thesis submitted in partial fulfillment of the requirements for the degree of Licenciaat in de Informatica

#### Abstract

Component-based development is a paradigm that explicitly emphasizes the reusability problem. Components are software pieces that are plugged together to form a program. Each component can be seen as a reusable part that can be plugged in other software compositions. Unfortunately embedded software has special characteristics (such as robustness, timing behaviour, ...), which compromise the reusability of such software. Therefore, components are not adapted to the characteristics common to embedded software. A real-time system runs software in which the correctness of the program depends not only on the logical results, but also on the time at which the results are produced. Timing constraints are used to specify the temporal corectness of the software. A real-time system is often concurrent by nature. A scheduler determines which concurrent process has priority over the others to keep up with the timing constraints. We use an adapted component model in which all component communication is asynchronous. This thesis proposes a way to extract semantic data from the component source code. The extracted data can be converted to a deterministic finite automata (DFA) which can be used by a finite state machine (FSM) to track the progress of the software. The information of the tracker can be used to make scheduling decisions on a single-processor embedded system. The techniques presented in this dissertation are a first step towards the reusability of software components in real-time embedded software.

## Contents

| Ι        | Des            | scribing Real-Time Behaviour                             | 3  |

|----------|----------------|----------------------------------------------------------|----|

| 1        | $\mathbf{Eml}$ | bedded Systems                                           | 5  |

|          | 1.1            | Definitions                                              | 5  |

|          | 1.2            | Characteristics                                          | 6  |

|          | 1.3            | Evolution in the Way of Developing                       | 7  |

|          |                | 1.3.1 Current Practices in Embedded Software Development | 7  |

|          |                | 1.3.2 Opportunities for Code Reuse                       | 8  |

|          | 1.4            | Problem Definition                                       | 8  |

|          | 1.5            | Approach                                                 | 9  |

|          | 1.6            | Summary                                                  | 11 |

| <b>2</b> | Con            | nponents and Reusability                                 | 13 |

|          | 2.1            | Definitions                                              | 13 |

|          | 2.2            | Components vs. Objects                                   | 14 |

|          | 2.3            | Plugging Components Together                             | 15 |

|          | 2.4            | Summary                                                  | 15 |

| 3        | The            | Component System                                         | 17 |

|          | 3.1            | Definition                                               | 17 |

|          | 3.2            | Tasks of a Component System                              | 17 |

|          | 3.3            | Component Communication                                  | 19 |

|          |                | 3.3.1 Shared Memory vs. Message Passing                  | 19 |

|          |                | 3.3.2 Synchronous vs. Asynchronous messages              | 20 |

|          | 3.4            | Levels of Concurrency                                    | 23 |

|          |                | 3.4.1 Component Interaction Concurrency                  | 24 |

|          |                | 3.4.2 Intracomponent Concurrency                         | 24 |

|          |                | 3.4.3 Intercomponent Concurrency                         | 24 |

|          | 3.5            | Internal Structure of the Component System               | 24 |

|          | 3.6            | Scheduling in the Component System                       | 27 |

|          | 3.7            | Summary                                                  | 28 |

iv CONTENTS

| 4 | Des | cribing the Abstract Behaviour of a Program                     | <b>29</b> |

|---|-----|-----------------------------------------------------------------|-----------|

|   | 4.1 | Message Sequence Charts                                         | 29        |

|   |     | 4.1.1 Introduction                                              | 29        |

|   |     | 4.1.2 Basic Message Sequence Chart                              | 29        |

|   |     | 4.1.3 High-Level Message Sequence Chart                         | 31        |

|   | 4.2 | Describing the Behaviour of a Program using MSCs                | 33        |

|   |     | 4.2.1 Problems with MSCs                                        | 33        |

|   |     | 4.2.2 Abstract MSCs vs. Concrete MSCs                           | 34        |

|   | 4.3 | Describing the Abstract Behaviour of a Component                | 34        |

|   |     | 4.3.1 Dealing with Programming Language Constructs              | 34        |

|   |     | 4.3.2 Describing Abstract Exceptions                            | 35        |

|   |     | 4.3.3 Distinguishing the Different Messages within a Com-       |           |

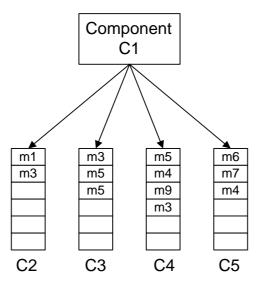

|   |     | ponent                                                          | 35        |

|   |     | 4.3.4 Describing Return-Messages                                | 38        |

|   |     | 4.3.5 Undetermined Interface Providers                          | 38        |

|   | 4.4 | Adding Message Parameters                                       | 39        |

|   | 4.5 | Refining the MSCs using the Parameters                          | 39        |

|   | 4.6 | Summary                                                         | 40        |

| 5 | Des | cribing the Concrete Behaviour of a Program                     | 43        |

|   | 5.1 | Resolving unknowns                                              | 43        |

|   |     | 5.1.1 Determining the Required Interface Providers              | 43        |

|   |     | 5.1.2 Determining the Clients of a Component                    | 44        |

|   | 5.2 | Making Exceptions Concrete                                      | 45        |

|   | 5.3 | Matching the Parameters                                         | 47        |

|   | 5.4 | Summary                                                         | 47        |

| 6 | Des | cribing Real-Time Behaviour                                     | 49        |

| • | 6.1 | Message Triggers                                                | 49        |

|   | 0.1 | 6.1.1 Evaluation of time-triggered software vs. event-triggered | 10        |

|   |     | software                                                        | 50        |

|   | 6.2 | Describing Message Triggers                                     | 51        |

|   | ٠   | 6.2.1 Aperiodic Messages                                        | 51        |

|   |     | 6.2.2 Periodic Messages                                         | 52        |

|   |     | 6.2.3 Sporadic Messages                                         | 52        |

|   | 6.3 | Dependencies                                                    | 53        |

|   | 6.4 | Specifying Time Constraints                                     | 53        |

|   | 0.1 | 6.4.1 Existing Syntax                                           | 54        |

|   |     | 6.4.2 Review of the Different Methods                           | 57        |

|   | 6.5 | Summary                                                         | 58        |

CONTENTS v

| II | $\mathbf{Sc}$ | heduling                                                 | 61          |

|----|---------------|----------------------------------------------------------|-------------|

| 7  | Scho          | edulability Analysis                                     | 63          |

|    | 7.1           | Execution Time                                           | 63          |

|    |               | 7.1.1 Problems with Measuring Execution Time             | 64          |

|    |               | 7.1.2 Expressing the Execution Time                      | 65          |

|    |               | 7.1.3 Test Sets                                          | 66          |

|    | 7.2           | Problem: Loops                                           | 67          |

|    |               | 7.2.1 Loops Embedded in Code                             | 68          |

|    |               | 7.2.2 Loops Encountered in Inter-Component Communication |             |

|    | 7.3           | Schedulability Test                                      | 70          |

|    | 7.4           | Summary                                                  | 73          |

| 0  | æ.            | 1. 41 E 4. C D                                           | <del></del> |

| 8  |               | cking the Execution of a Program                         | <b>75</b>   |

|    | 8.1           | Message-Based Tracking                                   | 75          |

|    | 8.2           | Constraint-Based Tracking                                | 76          |

|    | 8.3           | Requirements for Real-Time Software                      | 80          |

|    | 8.4           | Summary                                                  | 80          |

| 9  | Rea           | l-Time Scheduling                                        | 83          |

|    | 9.1           | Available Information                                    | 83          |

|    | 9.2           | Priority-Driven Scheduling Algorithms                    | 84          |

|    |               | 9.2.1 Static Scheduling Algorithms                       | 85          |

|    |               | 9.2.2 Dynamic Scheduling Algorithms                      | 85          |

|    |               | 9.2.3 Hybrid Scheduling Algorithms                       | 87          |

|    | 9.3           | Adjusting Thread Priorities using a DFA                  | 87          |

|    |               | 9.3.1 Time-Constrained Components                        | 88          |

|    |               | 9.3.2 Adjusting the priorities                           | 88          |

|    |               | 9.3.3 Scheduling using the Real-Time Behaviour           | 90          |

|    |               | 9.3.4 The Role of Refined MSCs                           | 92          |

|    | 9.4           | Scheduling with Queues                                   | 93          |

|    | 9.5           | Summary                                                  | 94          |

| 10 | Exa           | mple: A Real-Time Simulation                             | 95          |

|    |               | The Basic System                                         | 95          |

|    |               | Component Properties                                     | 95          |

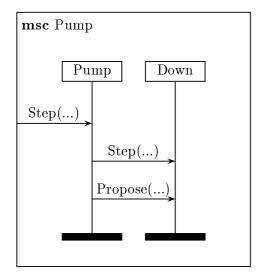

|    | 10.2          | 10.2.1 Pump Component                                    | 97          |

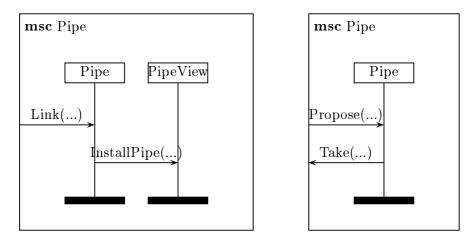

|    |               | 10.2.2 Pipe Component                                    | 97          |

|    |               | 10.2.3 Join Component                                    | 98          |

|    |               | 10.2.4 Graphical Components                              | 98          |

|    | 10.9          | Real-Time Parts                                          | 98<br>98    |

|    |               | Handling the Dependencies                                | 90<br>99    |

|    |               | Summary                                                  | 100         |

|    | TO.0          | Dummary                                                  | TOO         |

vi *CONTENTS*

| 11           | Mapping m Components onto n Threads            | 101        |

|--------------|------------------------------------------------|------------|

|              | 11.1 Context Switching                         | 101        |

|              | 11.2 Mapping Multiple Components onto 1 Thread | 102        |

|              | 11.3 Maintaining Schedulability                | 102        |

|              | 11.4 Summary                                   | 104        |

| 12           | Conclusion                                     | 105        |

|              | 12.1 Summary                                   | 105        |

|              | 12.2 Overall Conclusion                        |            |

|              | 12.3 Future Work                               | 108        |

|              | 12.3.1 Experiments                             | 108        |

|              | 12.3.2 Future Research                         | 108        |

| A            | Conversion of Constructs to MSCs               | 111        |

| В            | Abstract MSCs of Conduit Components            | 115        |

| $\mathbf{C}$ | Timing-Marked MSCs of ConduitSystem            | <b>121</b> |

## List of Figures

| 1.1  | Outline of this dissertation                                 | 10 |

|------|--------------------------------------------------------------|----|

| 3.1  | Shared Memory                                                | 20 |

| 3.2  | Synchronous (a) vs. Asynchronous (b) messages                | 23 |

| 3.3  | Levels of Concurrency                                        | 25 |

| 3.4  | Example message in Component Code                            | 26 |

| 3.5  | Logical Model of the Component Communication                 | 26 |

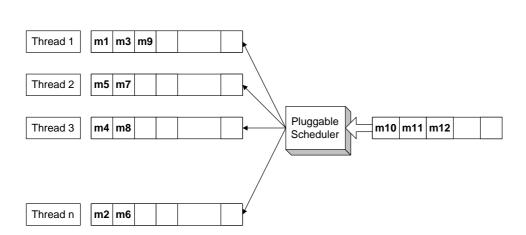

| 3.6  | Pluggable Scheduler                                          | 27 |

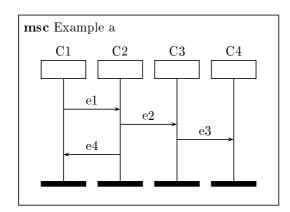

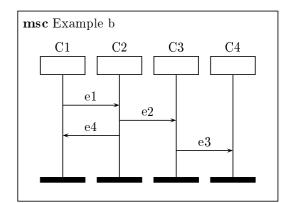

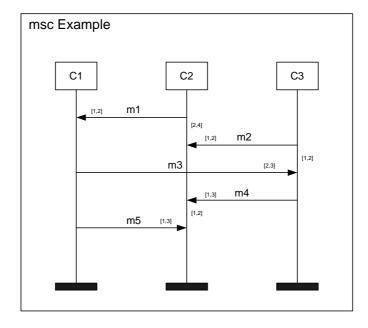

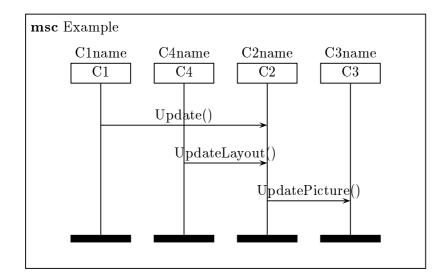

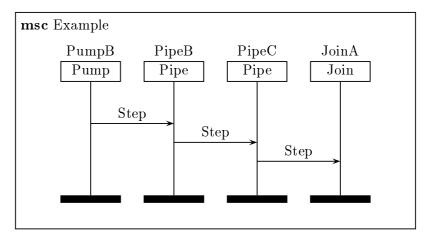

| 4.1  | Example of two equivalent basic MSCs                         | 30 |

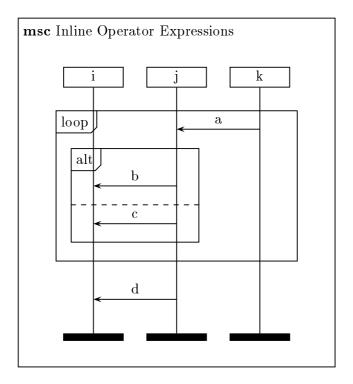

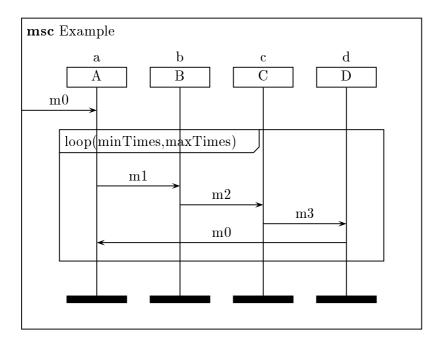

| 4.2  | Example of a basic MSC using inline operator expressions     | 31 |

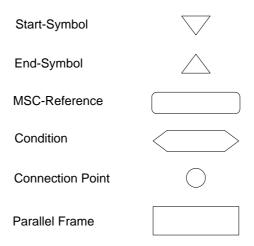

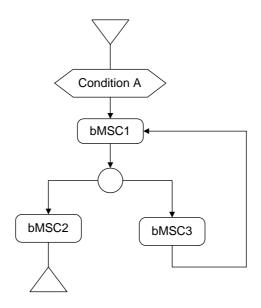

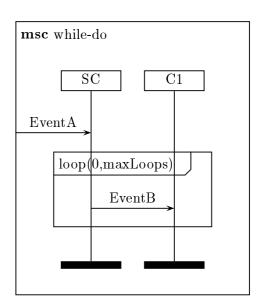

| 4.3  | Building Constructs of High-Level MSCs                       | 32 |

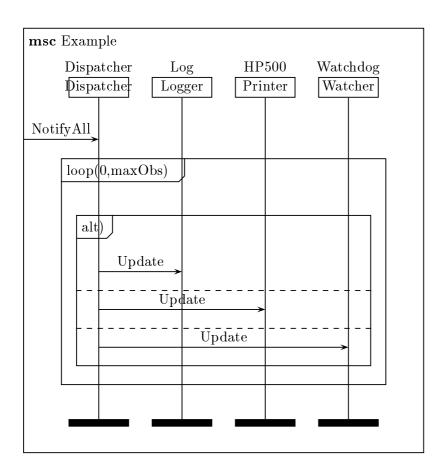

| 4.4  | Example of a High-Level MSC                                  | 32 |

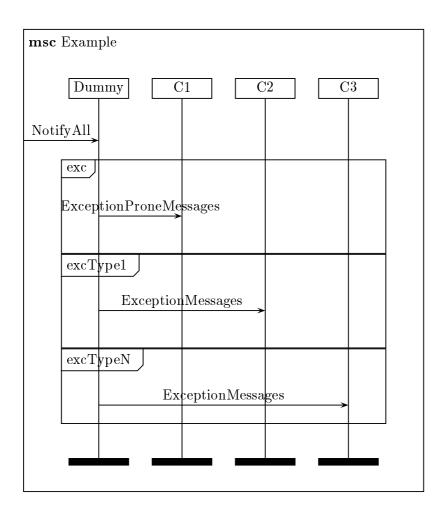

| 4.5  | Example of Exceptions in Component-Code                      | 36 |

| 4.6  | Abstract MSC describing exceptions                           | 37 |

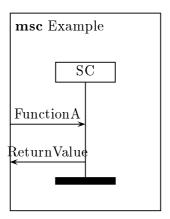

| 4.7  | Example of a Return Message                                  | 38 |

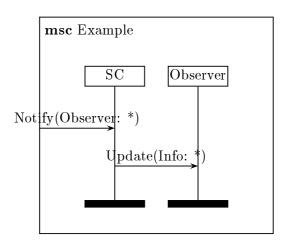

| 4.8  | Undetermined receivers                                       | 39 |

| 4.9  | Denoting Parameters on an MSC                                | 40 |

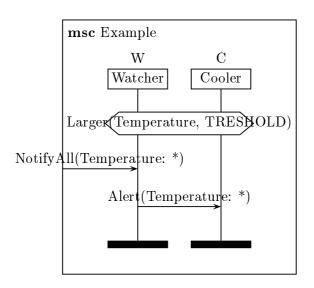

| 4.10 | Code from the Watcher Component                              | 41 |

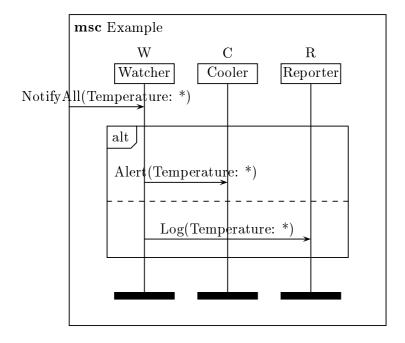

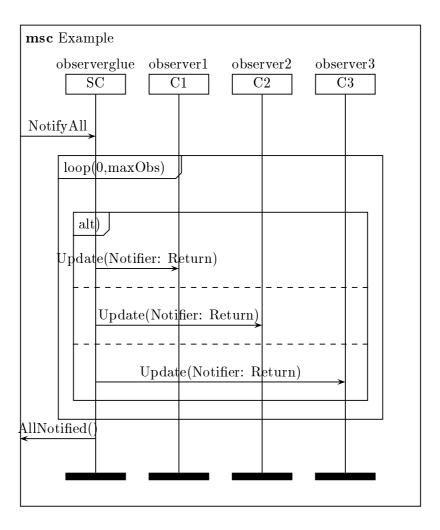

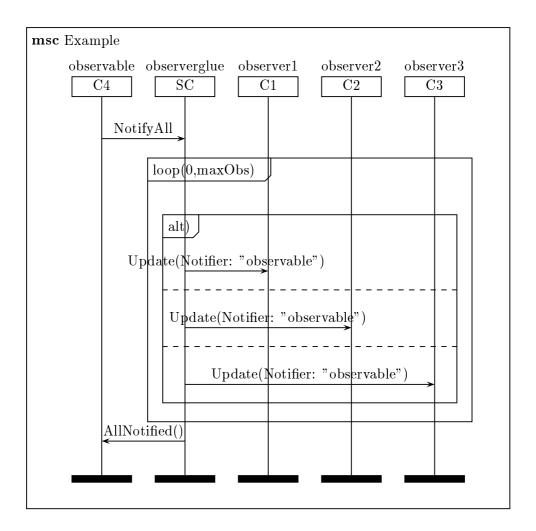

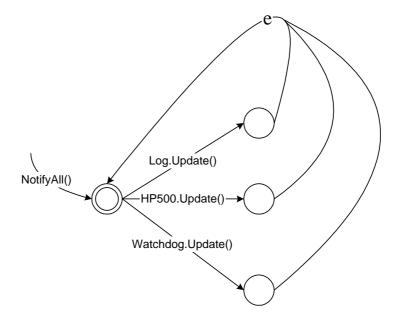

| 4.11 | Abstract MSC for Watcher.NotifyAll()                         | 41 |

| 4.12 | Refined MSC for Watcher.NotifyAll()                          | 42 |

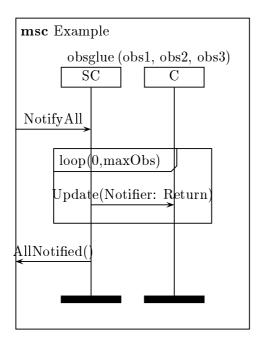

| 5.1  | Solution to Undetermined Receivers                           | 44 |

| 5.2  | Compact Solution to Undetermined Receivers                   | 45 |

| 5.3  | Solution to Undetermined Clients                             | 46 |

| 5.4  | Possible execution traces                                    | 46 |

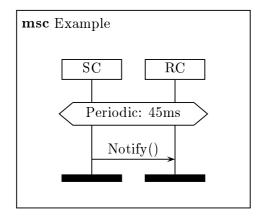

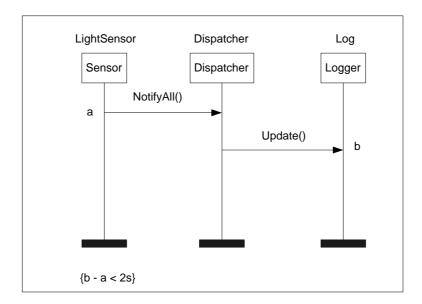

| 6.1  | Example: Aperiodic Message                                   | 52 |

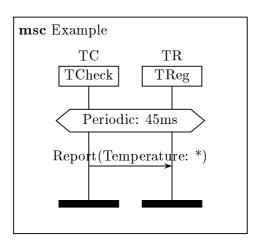

| 6.2  | Example: Periodic Message                                    | 52 |

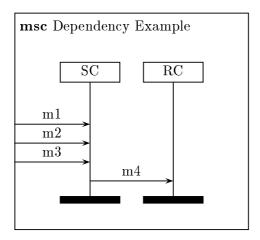

| 6.3  | Example: Describing Dependencies                             | 53 |

| 6.4  | Example of a basic MSC with timers                           | 55 |

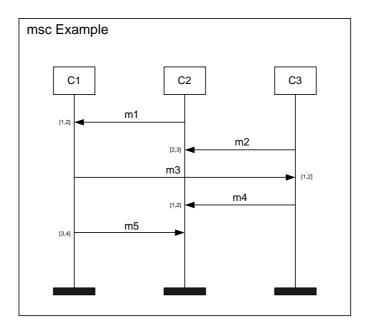

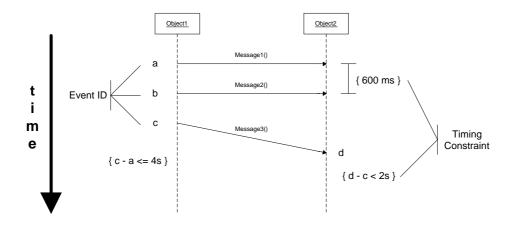

| 6.5  | Example of Event-associated Timing Constraints               | 56 |

| 6.6  | Example of Delivery Delays and Processor's Speed Constraints | 56 |

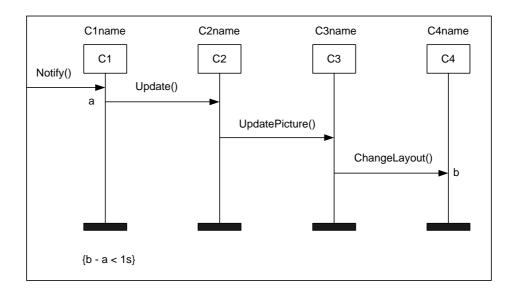

| 6.7  | Example of Time Constraints on UML Sequence Diagrams .       | 57 |

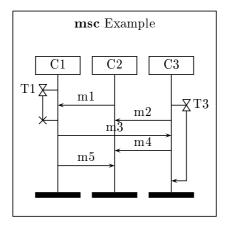

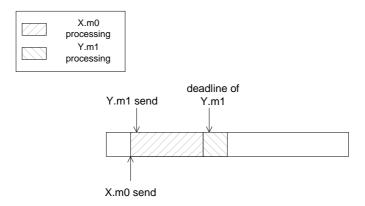

| 6.8                                           | Example of an MSC with timing markers                                                                                                                                                                                                                                       |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

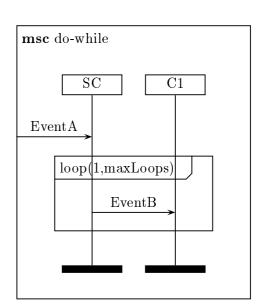

| 7.1<br>7.2<br>7.3<br>7.4                      | Documented Loops69Intercomponent Loops - Internal Queues70Documented Intercomponent Loops71Necessary Schedulability Test72                                                                                                                                                  |

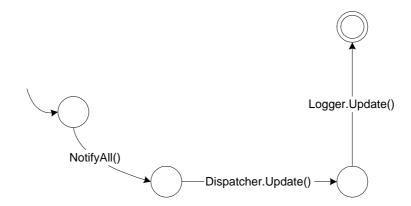

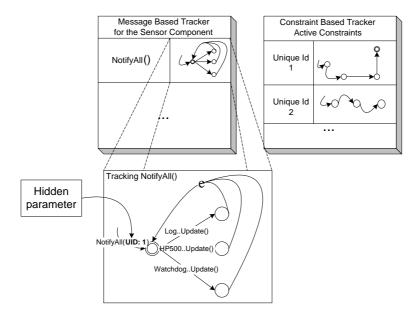

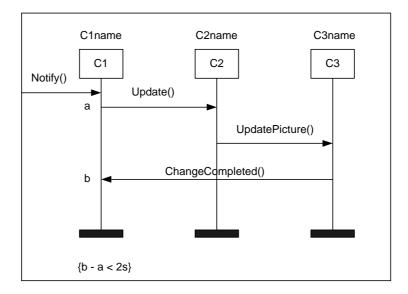

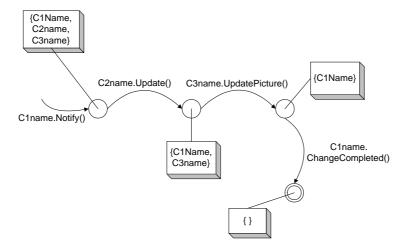

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5               | Example of a Concrete MSC77NFA corresponding to the Concrete MSC78Timing-marked MSC for the Logger79DFA of the Constraint80Relation between MBT and CBT81                                                                                                                   |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5               | Example of a Timing-marked MSC88DFA with the dependencies89Example: Dependent UpdatePicture() message91Example: Controlsystem of Nuclear Power Plant92Internal Queue Structure93                                                                                            |

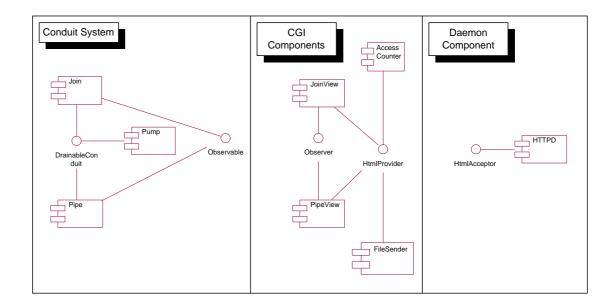

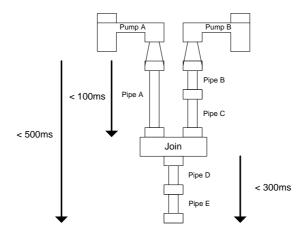

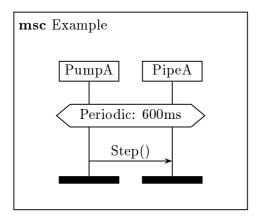

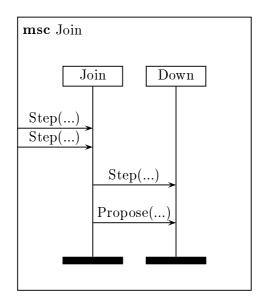

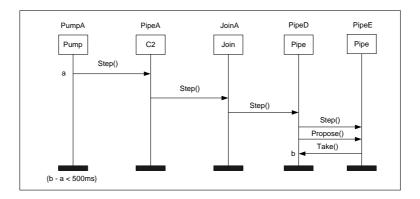

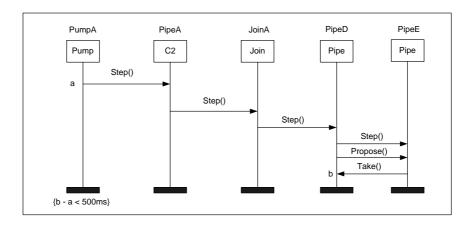

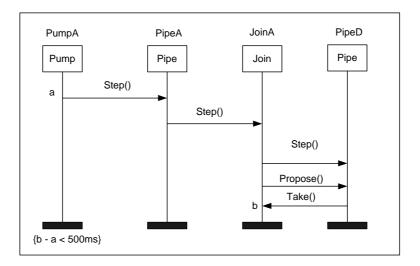

| 10.2<br>10.3<br>10.4<br>10.5                  | UML Component Diagram of the System96Configuration of the Conduit System96Periodic Step Message for Pump197Join: Dependencies98Timing-marked MSC for timing constraint100Dependent Path Computed for the Step() Message100                                                  |

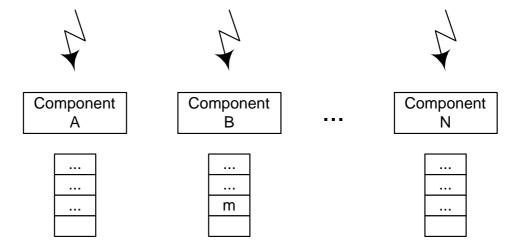

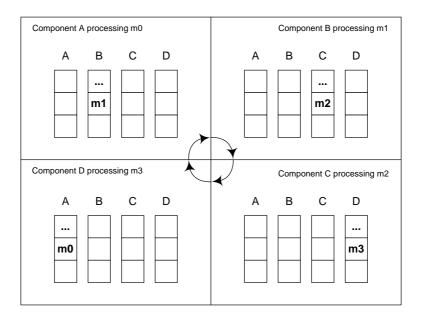

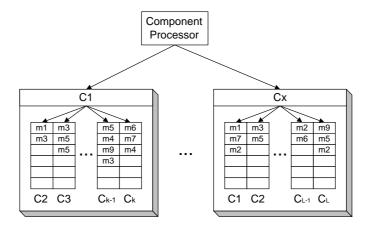

|                                               | Message Processor Concept                                                                                                                                                                                                                                                   |

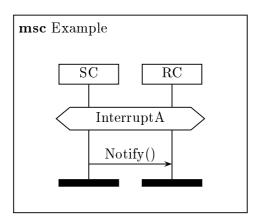

| A.1<br>A.2<br>A.3<br>A.4<br>A.5               | Conversion of if-then constructs                                                                                                                                                                                                                                            |

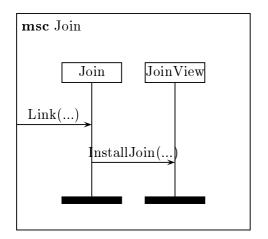

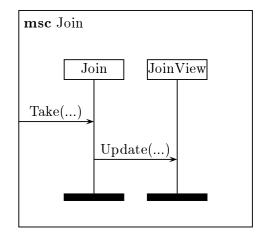

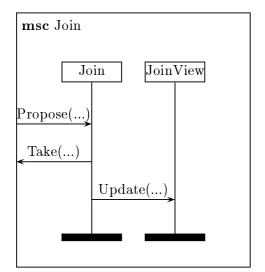

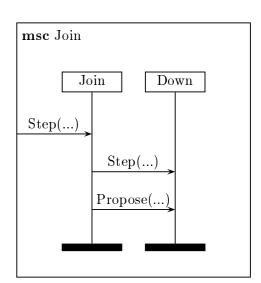

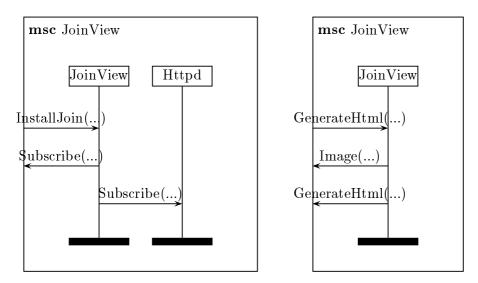

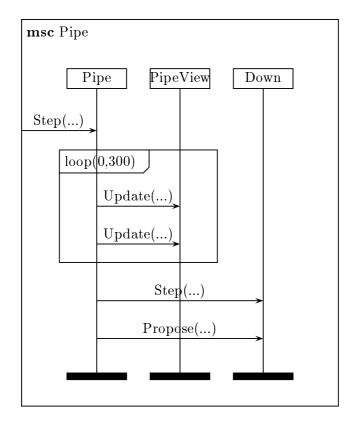

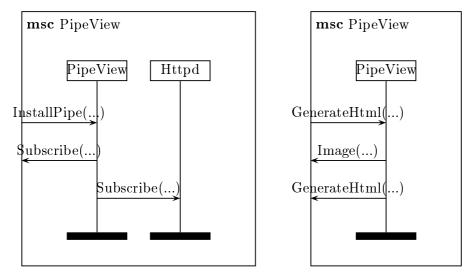

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7 | Join: Link-Take       116         Join: Propose-Step       116         JoinView: InstallJoin - GenerateHTML       117         Pump: Step       117         Pipe: Link-Propose       118         Pipe: Step       118         PipeView: InstallPipe - GenerateHTML       119 |

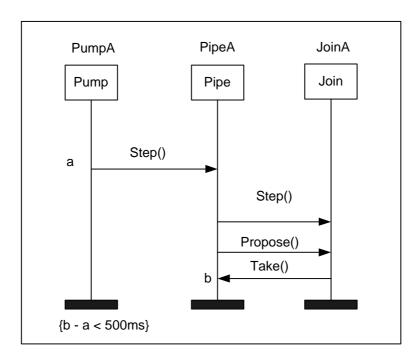

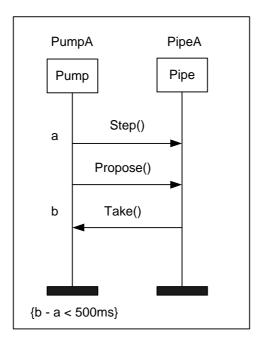

| C.1<br>C.2<br>C.3                             | Timing-marked MSC: PipeE needs to be updated within 500ms122 Timing-marked MSC: PipeD needs to be updated within 500ms122 Timing-marked MSC: JoinA needs to be updated within 500ms123                                                                                      |

LIST OF FIGURES ix

$\mathrm{C.4}$   $\,$  Timing-marked MSC: PipeA needs to be updated within  $500\mathrm{ms}\,123$

## List of Tables

|     | Comparison of Shared Memory vs. Message Passing Parameters Passed with Asynchronous Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1 | Mapping of Control Flow Structures to Inline Operator Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35       |

| 6.1 | Comparison of Event-triggered vs. Time-triggered Software $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($ | 51       |

|     | Sample List of the Average Execution Times Extra Information Needed for a Sufficient Schedulability Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72<br>72 |

| 9.1 | Dependent Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89       |

## Acknowledgements

This dissertation would not be what it is today, without the enormous amount of support that was given to me. Therefore I wish to express my gratitude towards:

Prof. Dr. Theo D'Hondt for promoting this dissertation

Werner Van Belle who came up with the subject and who helped me through every stage of this work from preparation through implementation and writing to proofreading. His comments and professional advise were very supportive and constructive.

Dr. Kim Mens, Dr. Tom Mens and Johan Brichau for proofreading my work and giving me valuable advise on both the content and the linguistics of this dissertation.

Holger Kenn for giving me advise about the time analysis of the component system.

The researchers of the Programming Technology Lab for listening and giving comments during the weekly presentations.

My parents for giving me the opportunity to study in the best possible circumstances and for being my best supporters.

The Vrije Universiteit Brussel for the excellent education.

# Part I Describing Real-Time Behaviour

### Chapter 1

## **Embedded Systems**

Embedded systems exhibit certain characteristics such as timing behaviour and high reliability demands, which have a great influence on the software development cycle. This chapter discusses these characteristics and how they have an impact on the development of embedded software. The chapter concludes with the exact contribution of this dissertation and an outline of the other chapters in this dissertation.

#### 1.1 Definitions

The word "embedded" can be used in different contexts which are loosely linked together, but each have a distinct meaning. As is common in the area of computer science there are often different versions of definitions for each term. The definitions we will use here are taken from [1, 2].

**Definition 1 (Embedded Processor)** Special features in respect to power-consumption, i/o-ports, and / or price of a processor are often used to denote a processor as being "embedded".

E.g., most of the microprocessors that are based on an ARM core are embedded processors.

**Definition 2 (Embedded System)** A computational device, which is strongly subject to physical constraints in its functional behaviour. It can for example be linked to a mechanical system or a chemical process, requiring timely responses obeying natural laws. Not only time, but also other factors like for example energy can be severe physical constraints.

E.g., an autonomous mobile robot.

**Definition 3 (Embedded Software)** Embedded software is software that runs on one or more processors embedded in a product and that is inextricably bound up with this product and its functionality. It cannot be bought separately, and it constitutes a large added value for the product.

E.g., software used in a mobile phone.

#### 1.2 Characteristics

Embedded systems can be recognized because they exhibit some characteristics that distinguish them from most desktop applications.

Robustness and Reliability Embedded systems have high reliability and robustness demands: Depending on the task performed by an embedded system, a failure in this system can be the cause of serious damage. E.g. the software that controls the airbags in your car, the software in a missile guiding system. Also, embedded software is difficult if not impossible to upgrade. Furthermore, the lifetime of embedded systems is often very long, which adds to the demands of robustness.

Time Constraints An embedded system typically interacts continuously with the surrounding environment and has to do this in a time-constrained manner. Most embedded systems exhibit a real-time behaviour. The very nature of real-time embedded applications makes certain characteristics of their implementation (such as timing and implementation architecture) critical. Usually, the software in these applications is responsible for the control of other equipment (e.g., mobile robots need real-time software to control the motor-sensor interactions).

Most real-time embedded systems are, by nature, multitasking solutions to real-world problems. The different parts of these systems usually run at different priorities and with different run-time characteristics. The notion of multiple tasks or threads being active in the system at the same time is common. Some of these real-time systems are deployed on a set of microprocessors in a distributed architecture.

Because real-time systems are the main topic of this dissertation we provided some clear definitions of the terms that are going to be used in the remainder of this dissertation:

**Definition 4 (Real-Time System)** a Real-time System runs software in which the corectness of the program depends not only on the logical results, but also on the time at which the results are produced.

E.g. a mobile robot.

**Definition 5 (Hard Real-Time System)** a Hard Real-Time System is a real-time system in which the lack of adherence to timing constraints results in a system that becomes useless and could result in a catastrophic system failure.

E.g. propulsion system of a space shuttle.

**Definition 6 (Soft Real-Time System)** a Soft Real-Time System is a real-time system in which the ability to meet deadlines is indeed required, but failure to do so does not render the system useless, nor does it cause a system failure.

E.g. a network router.

Resource Constraints Another important characteristic of embedded systems is the wide variety of critical metrics that must be taken into account in the software. These metrics include throughput, latency, program and data memory requirements, energy consumption, and financial cost.

#### 1.3 Evolution in the Way of Developing

A lot of progress has been made to the area of developing desktop application over the last decades, while the evolution of software development for embedded systems has made little evolution, because embedded software was so small and not interesting from a research point of view. Embedded software becomes complexer, because advanced processors and more memory becomes available at cheaper prices.

#### 1.3.1 Current Practices in Embedded Software Development

A lot of embedded software developers are still writing their software in low level languages such as C and assembly code, which makes the produced code error-prone, unreliable, difficult to read and therefore difficult to maintain. In a lot of embedded software development there is little or no reuse of existing code.

This is caused by several reasons of which some are mentioned here:

**Abstraction comes with a cost** Many developers believe that the use of data abstraction comes with a cost in performance. In the early days this assumption was true, but over the years the compilers have evolved and have become more efficient with each new release. Processors also provide more computational power at the same costs compared to a few years back.

**Diversity of hardware used in embedded devices** Code developed for a particular embedded system sometimes cannot be reused because a different chip architecture is used and the code does not compile for the new platform.

#### 1.3.2 Opportunities for Code Reuse

The opportunities for software reuse depend on the available resources in the embedded system. We can distinguish three different kinds of embedded systems based on the available resources.

- Severely constrained embedded systems have extremely limited resources available and perform mostly obvious tasks. Because of the limited memory it becomes impossible to use any high-level language and most of the software is developed using assembly code and C code. The functionality of such an embedded device is often also implemented in hardware instead of software. Example: a simple digital watch.

- Moderately constrained embedded systems have typically more complex software, which adds to the needs of having more resources available. The need for more complex software is mostly caused by the need of extra features on certain embedded devices. Examples: a television set, a set-top box, a digital camera, ...

- Loosely constrained embedded systems have resources available that can be compared or even exceed that of a regular Desktop PC. The development cycle of software for such an embedded system cannot be compared to that of a Desktop PC, because they are still inextrically bound with the hardware of the device. Besides that, the characteristics of robustness, high reliability demands and timing-behaviour still exist. Examples: control systems for nuclear power plants, control systems for industrial manufactoring.

It is obvious that there is little opportunity for code reuse in severely constrained embedded systems because these programs are so small due to the severe limitations on memory usage and CPU power. On the other hand moderately constrained and loosely constrained embedded systems could benefit from using a software development methodology that has reuse foremost in mind.

#### 1.4 Problem Definition

In the early days embedded systems were so small, that reuse of existing software was practically impossible. So with each new embedded system a new version of the software was written. Advanced processors and memory became cheap over the years, the embedded systems became more complex as well as the software. This increased complexity required research on a higher level for embedded systems.

Edward A. Lee [8] reduced most of this research to one question:

1.5. APPROACH 9

"How do we adapt the software abstractions designed merely to transform data to meet requirements like real-time constraints, concurrency and robustness?"

The SEESCOA (Software Engineering for Embedded Systems using a Component-Oriented Approach) consortium tries to find an answer to the question stated above using an adapted component-oriented approach. Members of this consortium are research teams from different flemish universities. There are two research groups of the VUB that participate in this consortium, namely the Programming Technology Lab and the System and Software Engineering Lab. Chapters 2 and 3 describe this adapted component-oriented approach and contain information from the deliverables [3] of the SEESCOA project.

In this dissertation we will focus on how we can do *soft* real-time scheduling for this adapted component-oriented approach, while trying not to harm the reusability principles of the independent components. Scheduling decisions will be made using semantic data extracted from the source code.

#### 1.5 Approach

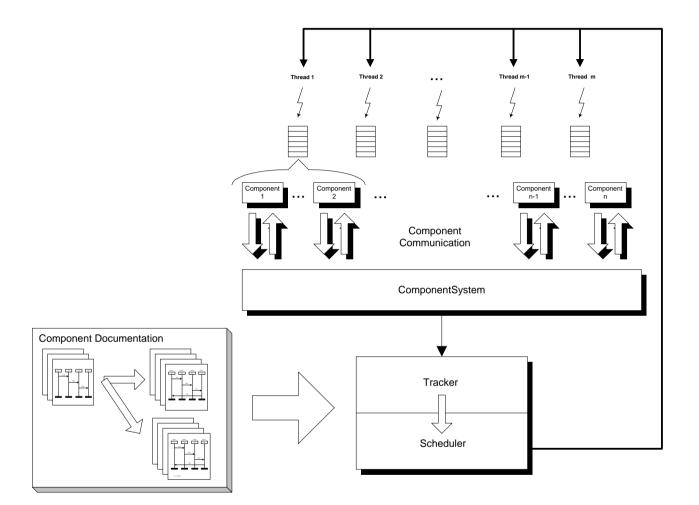

This section describes how this dissertation is organised. Figure 1.4 gives a total view on the outline of this dissertation.

- Chapter 2 gives a short introduction to components.

- Chapter 3 describes the implementation of the component system that is used throughout this dissertation and how it is adheres to the adapted component definition [10] proposed by the SEESCOA consortium. This chapter reflects the global view shown in figure 1.4.

- Chapters 4 and 5 propose a formal documentation format to describe the communication behaviour of the components. This is shown in figure 1.4 as the component documentation that is given as input to the tracker and the scheduler.

- In chapter 6 we discuss how to extend the documentation with information that is common to the characteristics of embedded software.

- Chapter 7 discusses measuring the execution times of components. It also describes how the documentation can be used together with the execution times to analyze the temporal behaviour of the software.

Figure 1.1: Outline of this dissertation

1.6. SUMMARY 11

• In chapter 8 we give an algorithm to follow the execution of a running system by matching the component interaction with the documentation. The tracker is encorporated in the scheduler component in figure 1.4.

- Chapter 9 describes how the tracker is used to enforce the temporal behaviour within the component system. In figure 1.4 this is represented with the line between the scheduler and the different threads.

- In chapter 11 we discuss how to reduce the overhead by reducing the number of threads in the component system, without affecting the temporal constraints of the embedded system. Represented with the brace between the threads and components in figure 1.4.

- Chapter 12 is a reiteration of the previous chapters. This chapter also discusses future work.

#### 1.6 Summary

Existing paradigms that support code reuse do not take the characteristics that are specific to embedded systems into account. The opportunities for code reuse depend on the available resources in the embedded system. This dissertation focusses on how we can make soft real-time scheduling decisions by using semantic data extracted from the source code.

## Chapter 2

## Components and Reusability

The latest paradigm that is used for software reuse is called *component* based development (CBD). Remember from chapter 1 that most research about embedded systems is to find an adapted software abstraction so that it meets the characteristics of the embedded systems. In this dissertation we adapt the CBD paradigm to meet these characteristics. Component based development is given preference to object-oriented development because a component is explicitly designed for reuse, which is not always the case for objects. Components are analogous to hardware components. For example, when a new television set is put together and the manufacturer chooses to replace the analogue tuner with a digital one, then the idea is to replace the software component controlling the analogue tuner with another version supporting a digital tuner. The adaptation of the software to the new hardware design can then happen by replacing one component, while reusing the other software components.

#### 2.1 Definitions

Throughout the rest of this dissertation we use some terms related to components. Because there exist many definitions and terms about components we describe what is meant by them in this section.

**Definition 7 (Component)** A component is a reusable documented software entity that is used as a building block for software systems. It is used to perform a particular function in a specific application environment within a specific component system. Components are composed (glued together) using their interfaces. These interfaces consist of provided interfaces and required interfaces.

As stated in the definition above a component has two kinds of interfaces: provided interfaces and required interfaces:

**Definition 8 (Provided Interface)** A Provided Interface describes the code signatures that must be used to access the services provided by the component.

Some components cannot provide their services without accessing services of other components.

**Definition 9 (Required Interface)** A required interface describes what services a component needs to be able to provide its services.

E.g. a component providing webservices needs the services of a network component to send the requested data over the network.

In the component definition a distinction has to be made between an abstract component and a concrete component.

**Definition 10 (Abstract Component)** An abstract component is a description of a reusable software element; it does not have a state. It also does not make sense to talk about the runtime properties of an abstract component.

**Definition 11 (Concrete Component)** A concrete component is an instantiation of an abstract component and has run-time properties.

The term component is more general; by using it we mean both aspects.

**Definition 12 (Interface Provider)** An interface provider is a component that is capable of providing the services defined by an interface, also sometimes called the implementor of an interface.

**Definition 13 (Client)** A component A that is using the services provided by component B is called a client of component B.

#### 2.2 Components vs. Objects

Concrete components are not objects. And in consequence, abstract components are not classes. First of all, components cannot inherit from other components. Objects do inherit from each other (they inherit the implementation). Abstract components are also extensively documented, which is not always the case for classes. Note that in some cases classes are documented with diagrams, semantics, call protocols, and so on, but this information is not explicitly described in the object definition. This information is often added in an informal way. When a component is implemented, it will probably use different objects to perform its functionality (of course in the case an OO language is chosen). Therefore some books talk about components as if they were big objects. This is true to some extent, but limiting the

component definition to this would be wrong. A concrete component should be thought of as having its own code and data space and also its own thread of control. This is necessary to have the ability to use different synchronization principles and make components reusable. Thinking a component has its own control flow will be more general than a component which enforces certain calling strategies upon other components. Or, a component written in the assumption its memory will be accessed by other components is more specific than a component which does not share its data using these kinds of techniques.

A component (the abstract as well as the concrete component) is always used in a certain application environment and in addition it also offers an application environment to its users.

#### 2.3 Plugging Components Together

When creating a program we need to puzzle over the different interfaces of the components. In a fully standardized world this could be done by just matching the correct interfaces of the different components. The real world, however, is not standardized at all, which implies that the component manufacturers invent names for the interfaces as they are needed. Because of this, different interfaces are provided for accessing the same services. Another problem that we are faced with is that when two components are communicating, data is passed along in the form of parameters. The format or types of these parameters needs to match as well. To overcome the problems stated above we need a bit of code to convert the parameters when components interact with each other. To match the different interfaces we can use the adapter pattern as described in [16]. The extra code that is needed to have a flawless communication between the components is called glue code.

#### 2.4 Summary

Software components are reusable software entities. They have the explicit guarantee that they are reusable in other software compositions. Components are however not adapted to the characteristics common to embedded software. In this chapter we have described how the components are adapted to match these characteristics.

## Chapter 3

## The Component System

This chapter starts by giving a rough definition of a component system. Afterwards we discuss what services should be provided by a component system for use in embedded systems. We conclude this chapter by looking more closely at how some of these services are satisfied in the component system that is used throughout this dissertation. Because component communication is one of the main services a component system provides we discuss on the different communication methods that can be used in a component system. As most embedded systems are concurrent, we talk about how concurrency can be introduced into the component system. Finally we discuss what services the component system provides in order to create a real-time system.

#### 3.1 Definition

The component system is the infrastructure (framework, architecture or kind of operating system), which makes component instances work together, which glues them and creates a homogenous environment for them. The component system can be seen as the middleware that connects different components and which makes them work together. To use a metaphor: the component system provides the streets while the components are the cars driving on it.

#### 3.2 Tasks of a Component System

This section gives a brief overview of the services a component system could provide to the components running on the system. These services are not always a requirement, it depends on the nature of the embedded system onto which the component system has to run. This is why we make the distinction between the required base services and the optional services.

#### **Base Services**

The component system

- Makes components work together. The component system should create and destroy component instances and be able to start and stop component instances.

- Abstracts the hardware and the operating system such that all components run in the same environment. For example, if we work in an embedded system with segmented memory or in a system with five flavors of memory access, the component system should solve this and offer a more or less flat interface to it. This abstraction should be as lightweight and as performant as possible in embedded systems. The component system should be mapped upon the operating system and programming language as closely as possible. It is not said that all hardware dependent issues should or could be put into the component system. All general hardware aspects that have impact on all of the code (like the memory access example) should be put into the component system. Modular hardware access, such as devices, can be put into separate components.

- Handles message passing between components: If a component wants to make another component do something, or whenever the state of another component has to be changed, a message is send to the component in question. Components must be able to send messages to other components using a reference (which can be obtained by using the unique name of the component). The component system takes care of sending data (over a network for example), calling the right function on components and eventually other ways of passing messages between components. This includes changing the data format if necessary, as is done in CORBA. Nevertheless, the component system is not necessarily a distributed environment.

- Provides some standard glue components to adapt interfaces between different components. For example, a certain component can return a callback with a specific name, whilst the receiver expects the message with another name. This can be handled by certain glue components.

- Intercepts hardware and software interrupts and models them as sending a message to the appropriate component handling the interrupt.

#### **Optional Services**

• Can have support for introspection. When working with components we need the ability to find, name and rename components. These

abilities could be provided by the component system. Furthermore, sometimes it is necessary that a client can query a component about its services. Mostly the client is bound to the components interface at client construction time (e.g. when the client is compiled). When introspection is possible, the client is not bound at client construction time, but it can dynamically (at runtime) find the services of a component. This can be compared to the reflection mechanism in Java and Smalltalk.

• Handles the scheduling between components. Because components are thought of as active entities it is necessary to map this view to a real operating environment. This is done by the component system, which ensures priorities of messages between components, which takes care of (hard) real-time constraints and scheduling in general.

#### 3.3 Component Communication

Components need to interact with each other for different reasons such as requesting services, notification of an event, etc... This happens through component communication, which is a base service of the component system. In this section we give a brief overview of how the different components can communicate with each other.

#### 3.3.1 Shared Memory vs. Message Passing

There are basically two ways in which components can communicate with each other: through shared memory and by sending messages.

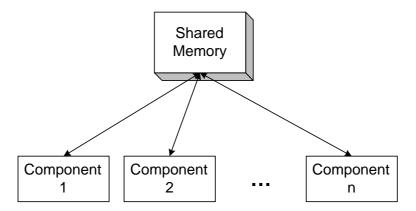

#### **Shared Memory**

In a shared memory architecture the different components have a common memory region in which data can be written and read (see figure 3.1). When component A wants to communicate information to component B it writes data to the shared memory and this data is then read by component B. Component B does not know when component A will have some data for him, so it will poll the memory at certain times. When memory is accessed by different concurrent processes, different situations can occur that can make the data in memory inconsistent. For example, when component A is writing data to the shared memory and component B starts writing data in the same memory region, the data could become inconsistent. Problems as these are solved by placing a lock before accessing the shared resource and removing the lock when the component is done accessing the shared resource. Placing locks is a good way of avoiding such problems, but makes the code prone to situations such as deadlocks and livelocks. Another disadvantage is

Figure 3.1: Shared Memory

|                    | Shared Memory | Message Passing |

|--------------------|---------------|-----------------|

| Efficiency         | +             | =               |

| Distributed access | -             | +               |

| Reusability        | -             | +               |

Table 3.1: Comparison of Shared Memory vs. Message Passing

that shared memory is hard to use in a distributed environment as memory is bound to a machine. There is some research done to use memory in a distributed environment [4]. One could also argue that the usage of shared memory conflicts with the idea of reusability. When we have a look at the different paradigms that were invented we see that shared memory is tried to be kept to a minimum. In procedural languages the use of local variables was recommended as much as possible. In object-oriented languages a step further is made by putting the data space with the operations onto that data into one encapsulated entity.

#### Message Passing

When component A needs to communicate with component B it could also send a message to component B. This message would then contain the information for component B. Message passing has the same overhead as a regular procedure call. When a message is passed, the parameters are put onto the stack and some call is made to component B.

#### 3.3.2 Synchronous vs. Asynchronous messages

Considering the different advantages and disadvantages of shared memory and message passing, the choice was made to do all component communication through message passing. All component communication is done through the communication layer of the component system. This layer is necessary to lookup the components' location on the system or on another system in a distributed environment. The layer is also used to provide information to the scheduler. There are two ways in which components could send messages among each other:

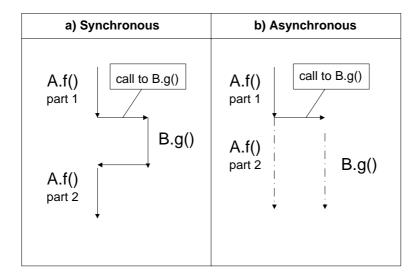

- Synchronous messages can be compared with regular method calls, so when component A sends a message to component B at some point, then component A is interrupted, component B processes the message and afterwards component A resumes (Figure 3.2 (a) on page 23). This kind of behaviour is the typical behaviour of most object-oriented and procedural programming languages.

- Asynchronous messages happen if component A sends a message to component B and component A does not wait until B has processed this message before continuing. This implies that component A and B can process their messages concurrently. Figure 3.2 (b) on page 23 shows an asynchronous method call on a single processor system. Asynchronous messages are used in actor-based languages [5].

The component system used in this thesis uses an asynchronous message model for all the intercomponent communication. Such a message model introduces concurrency into the component system implicitly. This has a number of advantages over an explicit thread based system:

**Communication** between concurrent parts happens through explicit messages and not through a shared data space. As noted earlier a shared resource can introduce subtle errors in a program.

**Semantic information** can easily be extracted from messages. We will explain later (see chapter 4) why this is important and how this can be done.

Mapping Using messages allows a customised mapping of components onto threads. Chapter 11 is dedicated to this subject.

**Safeness** Asynchronous messages are safer when used in distributed environments. When a computer crashes in synchronous communication, then the system is waiting for data that never comes resulting in a locked system.

But an asynchronous message model also has some drawbacks that need to be considered:

Return values When an asynchronous message m is sent by component A to component B, then component A does not wait until component B has processed that message and cannot get a return value. One of the reasons component A could have send a message to component B is to compute some value and then return that value. Hence when component B has computed that value it can send a message back to component A containing the return value. The problem now is that, while component A was awaiting that return value, it might have processed other messages that altered its state, making it impossible to use the return value in further computations. Situations like these are resolved by adding a special kind of parameter to the message m, namely a hidden parameter [6]. The semantics of a hidden parameter are as follows:

- When a component processes a message with a hidden parameter, then this parameter is send along with all messages that are sent while processing that message.

- Only the component that has put the hidden parameter in a message can access that parameter. This means the parameter is hidden for all other components.

Now when a component A sends message m to component B, it can put the state of that computation in a hidden parameter. When component B sends a return message with the computed value, the hidden parameter will be sent along. Component A can now access the hidden parameter, restore its state and continue with that computation.

**Extra code** Each time a component sends a message to a component that sends a message back with a return value, that component needs to provide code that:

- 1. Saves the state of the computation

- 2. Accepts the message containing the return value

- 3. Restores the state the computation

It is obvious that the extra amount of code causes the programming cycle to be prolonged and creates computational overhead.

Order of the messages When different asynchronous messages are sent to a component, then there is no guarantee in what sequence they will arrive at that component. This can cause several problems such as race conditions. Consider following example: A component provides access to a certain socket on a network interface. The component provides an interface to do the following three operations: OpenSocket, WriteToSocket and CloseSocket. A

Figure 3.2: Synchronous (a) vs. Asynchronous (b) messages

component accessing this component will typically first send an OpenSocket message followed by several WriteSocket messages and eventually request to close the socket. This example shows that the order of the incoming messages cannot be altered and should be preserved at all times. The component system assures that the order of the incoming messages is preserved.

#### 3.4 Levels of Concurrency

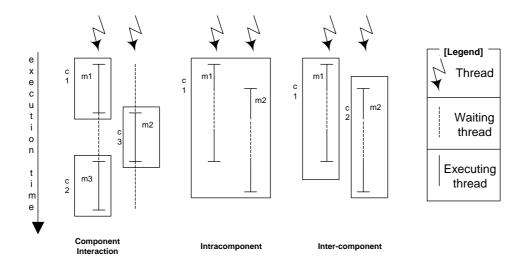

In embedded systems we often want to create a system that is able to react to events that happen in its environment. Most of the time the embedded system is performing other tasks when these events occur. When a system has to react to these events within a time bound we cannot always wait until the system has finished the other tasks. This is why many embedded systems have concurrent software. The Octopus methodology [7] describes three ways for introducing concurrency into an object-oriented system in a single processor architecture. Figure 3.3 comes from [7], but is adapted to components. These three distinctions can also be made in a component-based system:

- 1. Component interaction concurrency

- 2. Intracomponent concurrency

- 3. Intercomponent concurrency

#### 3.4.1 Component Interaction Concurrency

When a message for a component is processed, the component system chooses the message that is going to be processed next. After processing that message, another message is chosen for processing. Two messages cannot be processed simultaneously, so this is actually a single-threaded system. It is important to note that, when a message is being processed, it must complete before another message can be processed. Such behaviour is called non-preemptive (see figure 3.3). Component Interaction concurrency cannot be used in Real-Time Systems because it lacks pre-emptive concurrency. Pre-emptive concurrency is a requirement for a Real-Time System. It is obvious that when the processing time of a message is relatively long and a new time-constrained message occurs, the system is unable to process the message within the time boundaries. (Also see figure 3.3).

#### 3.4.2 Intracomponent Concurrency

In intracomponent concurrency a single component can process multiple messages concurrently (see figure 3.3). this kind of flexibility is not recommended because it can introduce subtle errors into the system (such as deadlocks, livelocks, etc...). This kind of concurrency also works by default on shared resources, which is the source of many of these problems mentioned above. These problems make the extendibility of a system difficult without introducing concurrency errors into the system.

#### 3.4.3 Intercomponent Concurrency

When a component is processing a message and a different component receives a message, then the message that is currently being processed can be interrupted or pre-empted to process the message received by the other component first (see figure 3.3). The distinction between component interaction concurrency and intercomponent concurrency comes from the fact that a message can be pre-empted for another message in intercomponent concurrency. Intercomponent concurrency is the kind of concurrency that is used in the component system to avoid the problems that were stated above. In a system using intercomponent concurrency the use of shared resources is avoided where possible. Because each component has its own resources it becomes easier to distribute the components onto different embedded systems that can communicate with each other.

#### 3.5 Internal Structure of the Component System

In section 3.3.2 we have advocated our choice for asynchronous communication between the different components. This section discusses how asyn-

Figure 3.3: Levels of Concurrency

chronous communication is achieved in the component system. Each component has a queue in which its incoming messages are placed. When component A sends a message m to component B, then the message m is placed in the queue of component B.